FPGA skills for the modern world

With the ever increasing number of applications involving video processing, AI or edge computing the appetite for suitably skilled FPGA Engineers has never been higher from the market which is expected to grow to $15 billion USD by 2027!

In terms of industries opportunities can be typically found within:

- Automotive

- Aerospace

- Defense

- Data Processing

However this list is certainly not exhaustive as any application requiring algorithms which can leverage from highly parallel and low latency compute, for example, are a natural fit for an FPGA.

The FPGA Engineer Mindset

Before diving into the modern day skillset required for an in demand FPGA Engineer we can discuss the mindset of an FPGA Engineer.

At a glance it may seem that an FPGA Engineer is equivalent to a Software Engineer as they also appear to be writing and testing code, however, to be a truly effective FPGA Engineer requires one to think in terms of the hardware they are trying to build, i.e. "Think Hardware".

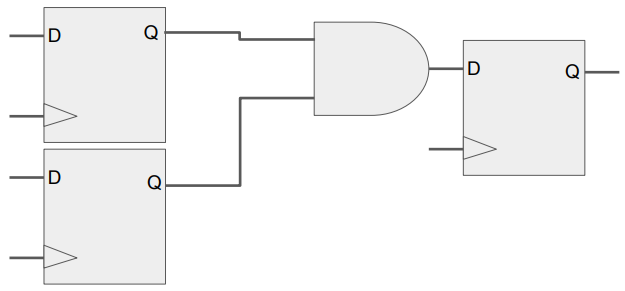

Shown above is a representation of a simple digital circuit that can be crafted with an FPGA that is often regarded as the Register Transfer Level or RTL of abstraction where we consider logic distributed within an FPGA between flip flops where processing occurs on each configured clock edge (typically positive). We describe this structure using a Hardware Description Language or HDL such as VHDL or Verilog. In a real world FPGA design we may have hundreds of thousands of these within the FPGA all running concurrently! This is the next foundational concept critical for FPGA Engineers where it must always be remembered that everything is running at the same time as we are working with hardware!

So far we have been thinking in terms of the hardware we wish to synthesize with all operations occurring concurrently as a result. This leads onto the next piece of mindset puzzle which is how do we debug these things? Well, as we are looking at hardware we can probe signals just as we would with an oscilloscope in the physical world which in the FPGA world we have Integrated Logic Analyzers or ILA's as below:

And so for FPGA's we are typically looking at waveforms when we debug to confirm a sequence of events match what we expect. To verify these sequences we cook up stimulation waveforms that we apply to our design which we probe the outputs. This system is known as the testbench of our design which falls under the verification bucket.

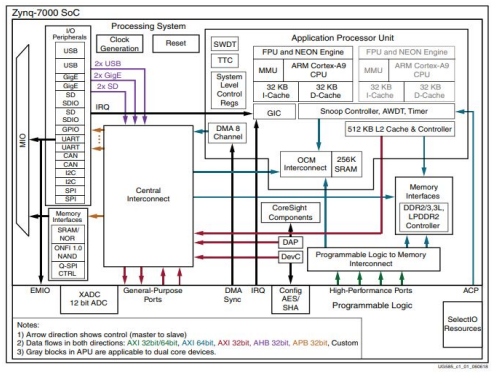

While the above is a solid base for an FPGA Engineer, there is a high demand for those that can understandv System on Chip or SoC systems such as the Zynq-7000, Zynq-Ultrascale or equivalent familes from other vendors which incorporate FPGA fabric with processor elements such as a dual Arm Core or most recently RISC-V. Related to these is an appreciation for incorporating the Linux Kernel into more complex applications within the processing system to leverage the vast array of middleware available for Linux.

RISC-V has become particularly relevant due to its licensing model (free and open!) and its capacity for custom instructions which can be used to accelerate operations.

Modern FPGA Skills

- Expertise with the two most common HDL languages - VHDL and Verilog

- Writing testbenches using SystemVerilog and UVM, VHDL and UVVM

- Writing testbenches using Python and cocotb (becoming more and more popular)

- Formal Verification

- Understanding of device trees and linux kernel drivers

- Understanding how to work with SoC's to leverage both the FPGA fabric and the PS

- Ability to think at the System Level (FPGA's often sit within complex systems)

- Understanding of the RISC-V ISA including custom instruction capabilities for acceleration

- Ability to work with on-chip bus topologies such as Wishbone, AXI and emerging such as Network On Chip or NoC's

- Ability to integrate a vast array of IP cores

- High speed design techniques and the nuances of clock domain crossing

- Reset and clocking strategies

- Comments

- Write a Comment Select to add a comment

To post reply to a comment, click on the 'reply' button attached to each comment. To post a new comment (not a reply to a comment) check out the 'Write a Comment' tab at the top of the comments.

Please login (on the right) if you already have an account on this platform.

Otherwise, please use this form to register (free) an join one of the largest online community for Electrical/Embedded/DSP/FPGA/ML engineers: