Grandiose Delusions

Recently on the MyHDL mailing-list there have been discussions about some other immature Python/HDL tools. In these discussion it was mentioned, how over the years, there has not been a strong set of open-source IP developed using MyHDL. For those that might be unfamiliar with the term IP (intellectual property) it is a term widely used in digital hardware to refer to reusable hardware components or blocks.

Many design languages have relied on that first big application before the language has gained wide adoption. The most notable example is ruby and ruby on rails. Even though there have been ASICs developed with MyHDL and commercial FPGA projects MyHDL is lacking open-source IP - its ecosystem -.

But why is this so? MyHDL is a perfect platform for developing IP for many reasons.

- Power of Python!

- Strong verification features (verification becomes fun)

- Single language for algorithm and hardware development

- Can generate Verilog or VHDL

(see Why MyHDL for more examples)

Over the years I have started a bunch of IP development myself but never really completed much. I wanted to reflect why, I had some motivation and a really good tool (that being MyHDL) but I didn't quite reach a goal of creating usable open-source IP. Why have I been unsuccessful? I believe the title of this blog captures it. I usually start off with some large project but fail to appreciate the effort required to create high quality IP. Which in a way, is crazy because this is partially what I do for a living! But I work on these projects in my free time and I manage my free time much differently than my work time.

What do I consider high quality? To me high quality is well documented (i.e. straight-forward to use by someone verse in digital system design), full verification, and hardware tested. It takes some planning and determination to put a project together of this scope.

As mentioned, I work on these projects in my free time and that is my main excuse (flaw). When I am 'working' on these projects in my free time (which seem to be nil these days between work on family) I often lack the discipline to finish something. I am more often than not, 'playing'/'hacking', than doing structured project development.

I have created a couple pieces of IP that others have found useful, an IIR filter and a FFT core. But both of these lack good documentation and regression tests.

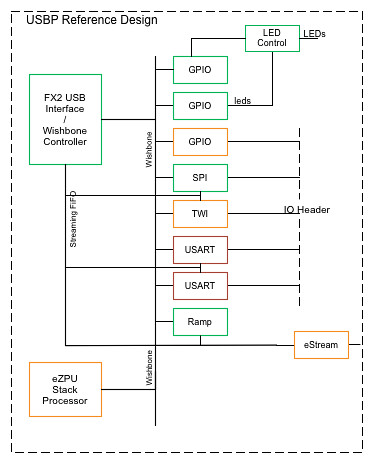

Other IP that I have worked on is creating a bunch of the basic blocks in a digital system to be used on a USB FPGA board. The following is a diagram of the IP I was developing for the USB FPGA project.

Most of these blocks by themselves are fairly basic. In this system the blocks are accessible similar to the hardware components in a microcontroller system. The USB interface exposes a simple address read/write interface and blocks can be controlled externally by a PC. As depicted in the above diagram the blocks were implemented to be compatible with the wishbone interface.

I had completed a bunch of the blocks as illustrated by the green outline. The orange are blocks with significant progress and the red were blocks that I decided I wanted but hadn't started. I never found the motivation to bring these to completion (man.o.man). Time willing I will move these to a public repo soon and try to document (but I wouldn't hold my breathe).

Related to "managing my free time", when developing IP I often am distracted creating more "tools". Python/MyHDL is this great environment for developing IP and tools. An example of building more tools; while creating the blocks above I needed register definitions for each block. What I wanted to do is simply define the register set in a Python dictionary and have a module that would use the dictionary definition and create the wishbone register interface. Below is an example of a single register definition for an SPI module (note: I use IP, block, module, core all interchangeably).

RegDef["SPCR"] = \

{"addr" : 0x60, "width" : 8, "type" : "rw",

"bits" : {"loop" : {"b" : 0, "width" : 1, "comment" : "Internal loopback"} ,

"spe" : {"b" : 1, "width" : 1, "comment" : "System enable"} ,

"cpol" : {"b" : 3, "width" : 1, "comment" : "Clock Polarity"} ,

"cpha" : {"b" : 4, "width" : 1, "comment" : "Clock Phase"} ,

"msse" : {"b" : 5, "width" : 1, "comment" : "Manual slave select enable"},

"freeze" : {"b" : 6, "width" : 1, "comment" : "freeze the core"},

"wb_sel" : {"b" : 7, "width" : 1, "comment" : "1 = wishbone bus feeds the TX/RX fifo."+

"Else the streaming interface feeds FIFOs"},

},

"default" : 0x98, # CPOL = CPHA = WB_SEL = 1

"comment" : "SPI Control register"

}

In a block implementation, I only needed to pass the wishbone signals, dictionary register definition, and would get a list of signals for the read/write registers and read-only registers.

regFile = RF.RegisterFile(clk_i, rst_i, cyc_i, stb_i, adr_i, we_i,

sel_i, dat_i, dat_o, ack_o,

rwRegisters, rwWr, rwRd, roRegisters, roRd,

RegDef = RegDef,

C_WB_BASE_ADDR = C_WB_ADDR)

With Python and its ecosystem I have a plethora of tools to dump the register definitions to different formats, HTML, pdf, etc. I can also easily create GUIs to define the register sets and/or import XML definitions like IP-XACT. Even though it was fun and useful to define this register tool it did distracted me from finishing the project. I could have simply defined each register set in the blocks and been on my way.

One of the things the MyHDL community needs is a place to dump projects. Something simliar to open-cores but a site that can leverage the power of python, example running the tests for each of the blocks periodically. But setting up a site to host the projects is a whole other set of issues and distraction. I don't see it happening anytime soon. Anyone that has developed projects with MyHDL are invited to share their projects on the MyHDL wiki. But that is only good for a brief description and not a solution for hosting the code.

In conclusion, there are many folks working on projects and developing IP using MyHDL so hopefully they will be more successful at finishing a project and making it available than I have been.

- Comments

- Write a Comment Select to add a comment

To post reply to a comment, click on the 'reply' button attached to each comment. To post a new comment (not a reply to a comment) check out the 'Write a Comment' tab at the top of the comments.

Please login (on the right) if you already have an account on this platform.

Otherwise, please use this form to register (free) an join one of the largest online community for Electrical/Embedded/DSP/FPGA/ML engineers: